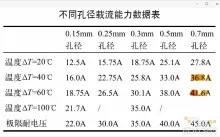

实测 | PCB走线与过孔的电流承载能力到底有多强?

<strong>简介:</strong>

使用FR4敷铜板PCBA上各个器件之间的电气连接是通过其各层敷着的铜箔走线和过孔来实现的。

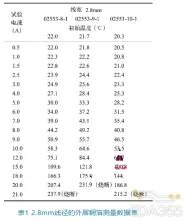

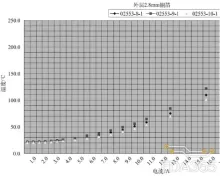

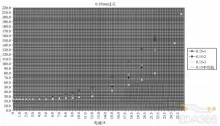

由于不同产品、不同模块电流大小不同,为实现各个功能,设计人员需要知道所设计的走线和过孔能否承载相应的电流,以实现产品的功能,防止过流时产品烧毁。

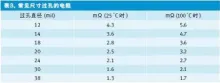

文中介绍设计和测试FR4敷铜板上走线和过孔的电流承载能力的方案和测试结果,其测试结果可以为设计人员在今后的设计中提供一定的借鉴,使PCB设计更合理、更符合电流要求。

<strong>1、引言</strong>

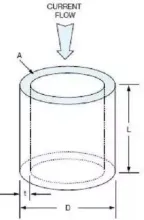

现阶段印制电路板(PCB)的主要材料是FR4的敷铜板,铜纯度不低99.8%的铜箔实现着各个元器件之间平面上的电气连接,镀通孔(即VIA)实现着相同信号铜箔之间空间上的电气连接。

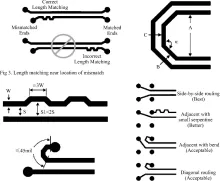

但是对于如何来设计铜箔的宽度,如何来定义VIA的孔径,我们一直凭经验来设计。

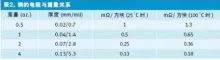

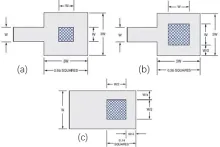

为了使layout设计更合理和满足需求,对不同线径的铜箔进行了电流承载能力的测试,用测试结果作为设计的参考。

PCB设计当中 走线 的设计规范

<font color="#FF0000">作者: 郑振宇</font>

上一期我们和大家分享了 “<a href="http://mouser.eetrend.com/blog/2019/100017863.html">PCB设计当中 过孔 的设计规范</a>” 这一期我们再继续来分享这篇 PCB设计当中 走线 的设计规范

1、为满足国内板厂生产工艺能力要求,常规走线线宽≥4mil(0.1016mm) (特殊情况可用3.5mil,即0.0889mm);小于这个值会极大挑战工厂生产能力,报废率提高。

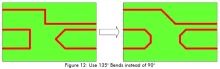

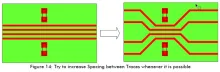

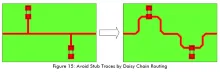

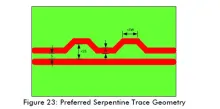

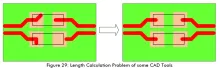

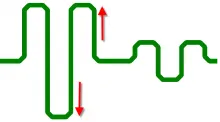

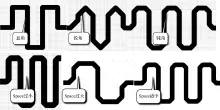

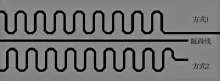

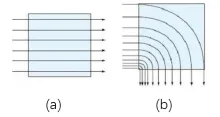

2、走线不能出线任意角度走线挑战厂商生产能力,很多蚀刻铜线时候出现问题,推荐45°或135°走线,如图1-1所示。

开关电源中的12种“地”的布局与走线!

<strong>摘要 </strong>

Ⅰ、 地”的概念

Ⅱ、开开关电源中“地”的分类

Ⅲ、开关电源中接地的方式

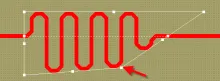

Ⅳ、实际布线中关于 “地 ”的考虑

Ⅴ、总结

<strong>“地”的概念</strong>

Ⅰ、定义

作为电路或系统基准的等电位点或平面

Ⅱ、符号

<center><img src="http://mouser.eetrend.com/files/2019-01/%E5%8D%9A%E5%AE%A2/100017390-58…; alt=“”></center>

Ⅲ、作用

不同种类的接地作用各异

Ⅳ、关于“ 地”的思考

●理想地线应是一个零电位、零阻抗的物理实体

分页

- 页面 1

- 下一页