珠海錾芯半导体基于自有EDA软件ZESTOPT显著提升Transformer硬件PPA(Power, Performance, Area)。

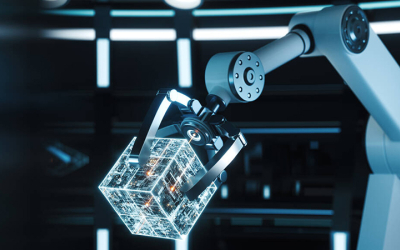

图1:ZESTOPT和Synopsys DC 生成的SwfitTron Transformer芯片面积和时钟周期

图1中红色→箭头所示,最高性能提升59.7%, 同时芯片面积减小19.2%。

图1中蓝色→箭头所示,实现Synopsys DC最高芯片性能,面积减少54.4%。

图1中以最小芯片面积,性能提升60%,如图中紫色→箭头所示。

图1中在最小芯片面积的基础上,增加10%芯片面积,性能提升166.7%,如图中绿色→箭头所示。

图1中作为对比的蓝色曲线是Synopsys Design Compiler实现的芯片面积和对应的时钟周期。

图1中红色曲线是錾芯自有EDA软件ZESTOPT在Synopsys Design Compiler基础上进一步优化,并由Synopsys Design Compiler输出的结果。

图1中Transformer硬件设计来自SwiftTron: An Efficient Hardware Accelerator for Quantized Transformers, by A.Marchisio et al., in Joint Conference on Neural Networks, June 2023。

EDA软件ZESTOPT优化结果

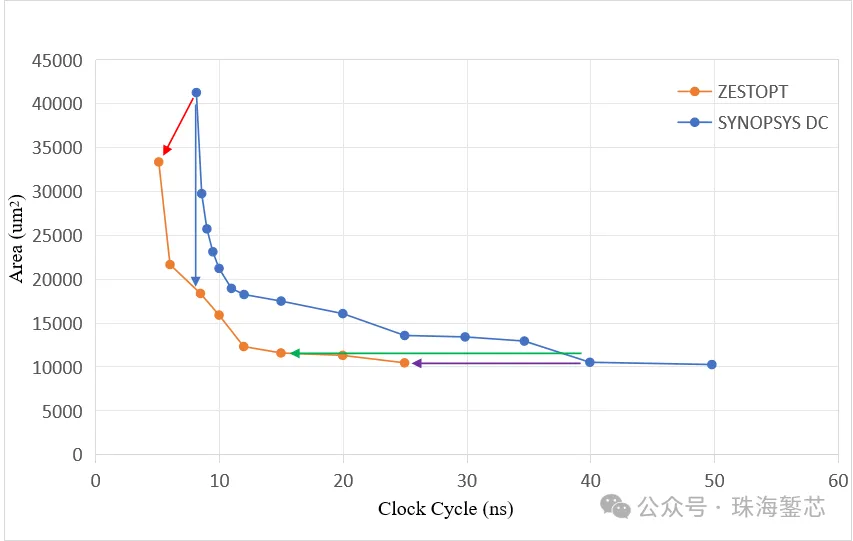

1. 对于RISC-V:

以相同最小面积提升性能50%,如图2红色→箭头所示;

或者减小最小面积5.3%,同时提升性能14.3%,如图2黑色→箭头所示。

图2:ZESTOPT和Synopsys DC生成的RISC-V芯片面积和时钟周期

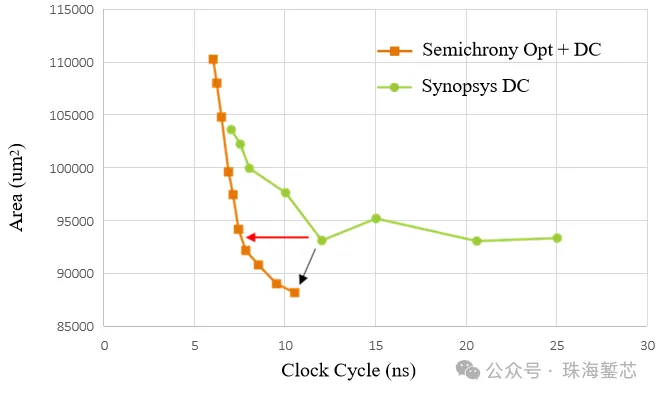

2. 对于DSP信号处理单元(即AI芯片中乘加阵列的基本运算单元):

以小11.2%的芯片面积提升最高性能68.7%,如图3红色→所示;

相同芯片性能@741MHz,面积减小34.4%,如图3蓝色→所示;

相同芯片面积,性能提升63.5%(628MHz→1.03GHz),如图3紫色→所示。

图3:ZESTOPT和Synopsys DC生成的DSP数字信号处理/AI乘加陈列的芯片面积和时钟周期

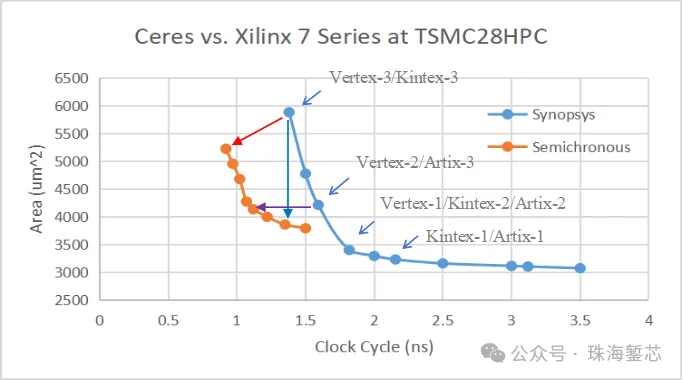

珠海錾芯半导体有限公司成立于2021年12月,主营业务包括FPGA芯片,PCB板卡,EDA软件租赁和设计服务。錾芯28纳米FPGA在对标赛灵思基础上,实现功能增强和性能提升。錾芯以其独有专利技术致力于通过新一代高性能集成电路设计方法提供工艺迭代之外另一条实现高能效大算力芯片的技术路径。现有技术在28纳米工艺上实现传统集成电路在7纳米工艺上的性能。

本文转载自:珠海錾芯