1. 智多晶 XSTC_8B10B IP

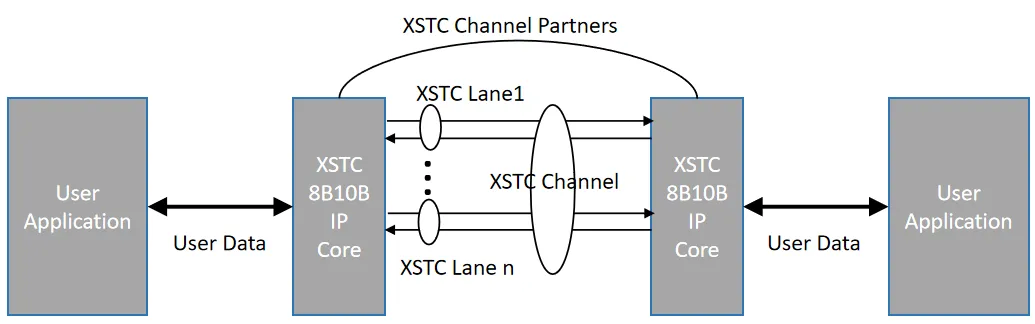

XSTC_8B10B IP(XSTC:XiST Transmission Channel)是智多晶开发的一个灵活的,轻量级的高速串行通信的IP。IP在具备SerDes(单通道或多通道)高速串行收发器之间构建出接口简单,低成本,轻量化的高速率数据通信通道,其系统如图 1-1所示:

图 1-1 XSTC_8B10B 系统概图

XSTC_8B10B IP自动初始化通道并维护通道的连接。XSTC通道伙伴是通信的两端,在通道间可以自由的传输数据。XSTC帧的长度是任意的,能在任意时间被打断。在有效数据间的间隙会自动插入的空闲来保持锁定和防止过度的电磁干扰。流控能用来降低传入的数据速率或通过信道发送简短的高优先级消息。

在没有数据时,空闲被发送来保持链路激活。XSTC_8B10B IP使用8B10B的编解码规则来探测单比特和多比特错误。过多的比特错误,断开连接,设备故障会导致IP断开复位并尝试重新初始化通道。

2. 典型应用场景

XTSC_8B10B IP 能广泛使用:

芯片-芯片连接:使用高速串行连接替代并行总线的连接,IP要求FPGA必须有SerDes高速串行收发器。

板-板和背板连接:IP能在速率和通道宽度上灵活配置,并在高性能系统中使用。

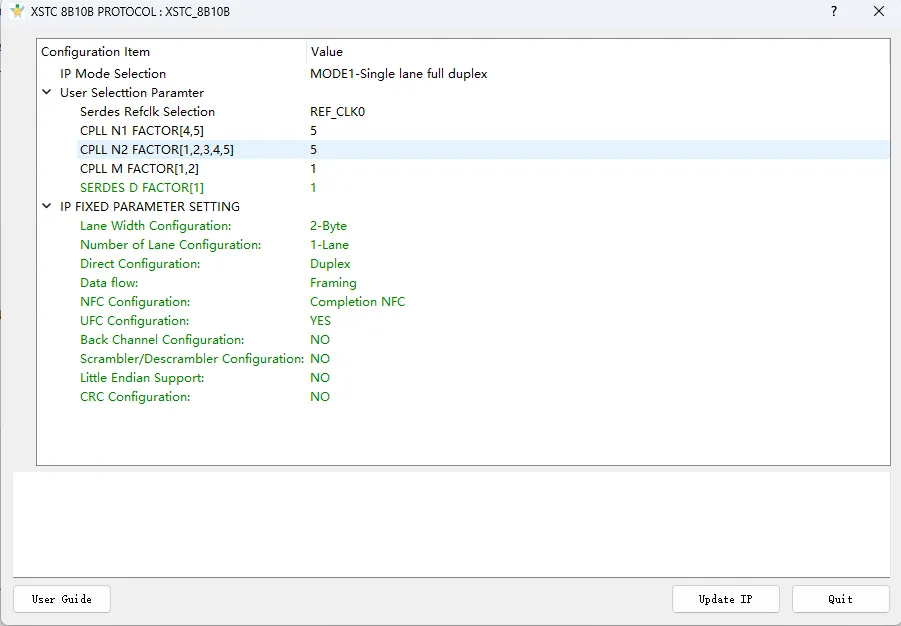

XSTC_8B10B IP用户文档已随IP发布,可通过IP界面左下角的用户指南打开文档,内有IP详细使用说明。

文章来源:智多晶