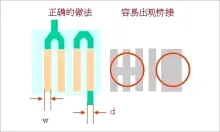

PCB上的立碑不良缺陷

PCB上的立碑(tombstone)也叫曼哈顿吊桥或吊桥效应等,是一种片式(无源)元器件组装缺陷状况,其成因是零件两端的锡膏融化时间不一致,而导致片式元件两端受力不均,这种片式元件自身质量比较轻,在应力的作用下就会造成一边翘起,形象的称之为立碑。

<center><img src="http://mouser.eetrend.com/files/2021-01/博客/100060778-118652-1.jpg" alt=“” width="600"></center>

也许纯文字描述大家不太好理解,老wu这里分享一份SMT 立碑现象发生过程的视频供大家参考。

PCB的板级去耦设计方法和实例讲解

<strong>一,什么是PCB中的板级去耦呢?</strong>

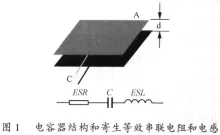

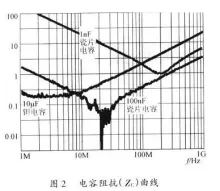

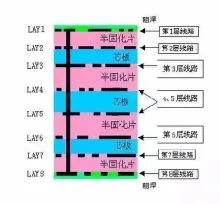

板级去耦其实就是电源平面和地平面之间形成的等效电容,这些等效电容起到了去耦的作用。主要在多层板中会用到这种设计方法,因为多层板可以构造出电源层和地层,而一层板与两层板没有电源层和地层,所以设计不了板级去耦。

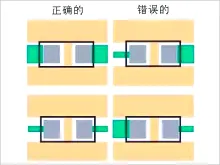

<strong>二,如何设计板级去耦?</strong>

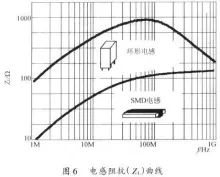

多层板pcb在设计板级去耦时,为了达到最好的板级去耦效果,一般在做叠层设计时把电源层和地层设计成相邻的层。相邻的层降低了电源、地平面的分布阻抗。从平板电容的角度来分析,由电容计算公式C=εs/(4πkd)可以,两平板之间的距离d越小,电容值越大,相当于加了一个大的电解电容,相邻的层两平面的d是最小的,所以电源层和地层设计成相邻的层,可以达到最好的去耦效果。

<strong>三,实例分析</strong>

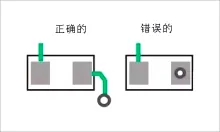

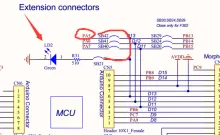

1.设计四层板时,中间两层分别是电源板和地层