七大步骤教你确定PCB布局和布线

PCB(Printed Circuit Board),中文名称为印制电路板,又称印刷电路板、印刷线路板,是重要的电子部件,是电子元器件的支撑体,是电子元器件电气连接的提供者。由于它是采用电子印刷术制作的,故被称为"印刷"电路板。

PCB(Printed Circuit Board),中文名称为印制电路板,又称印刷电路板、印刷线路板,是重要的电子部件,是电子元器件的支撑体,是电子元器件电气连接的提供者。由于它是采用电子印刷术制作的,故被称为"印刷"电路板。

随着PCB 尺寸要求越来越小,器件密度要求越来越高,PCB 设计的难度也越来越大。如何实现PCB 高的布通率以及缩短设计时间,在这谈谈对PCB 规划、布局和布线的设计技巧。

在开始布线之前应该对设计进行认真的分析以及对工具软件进行认真的设置,这会使设计更加符合要求。

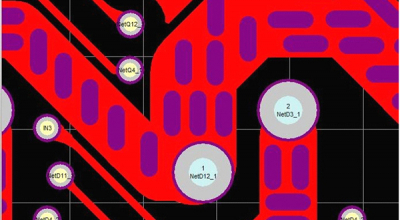

1、确定PCB 的层数

Cadence Allegro现在几乎已成为高速板设计中实际上的工业标准,最新版本是Allegro 16.5。与其前端产品Capture相结合,可完成高速、高密度、多层的复杂 PCB 设计布线工作。

Allegro操作方便、界面友好、功能强大,如仿真方面,信号完整性仿真、电源完整性仿真都能做。

PCB板的设计是电子工程师的必修课,而想要设计出一块完美的PCB板也并不是看上去的那么容易。一块完美的PCB板不仅需要做到元件选择和设置合理,还需要具备良好的信号传导性能。本文将会就PCB高速信号电路设计中的布线技巧知识,展开详细介绍和分享,希望能够对大家的工作有所帮助。

一、合理使用多层板进行PCB布线

在进行PCB布线时,经常会发生这样的情况:走线通过某一区域时,由于该区域布线空间有限,不得不使用更细的线条,通过这一区域后,线条再恢复原来的宽度。走线宽度变化会引起阻抗变化,因此发生反射,对信号产生影响。

那么什么情况下可以忽略这一影响,又在什么情况下我们必须考虑它的影响?

有三个因素和这一影响有关:

1、阻抗变化的大小;

2、信号上升时间;

3、窄线条上信号的时延。

首先讨论阻抗变化的大小,很多电路的设计要求反射噪声小于电压摆幅的5%(这和信号上的噪声预算有关),根据反射系数公式:

ρ=(Z2-Z1)/(Z2+Z1)=△Z/(△Z+2Z1)≤5%可以计算出阻抗大致的变化率要求为:△Z/Z1≤10%你可能知道,电路板上阻抗的典型指标为+/-10%,根本原因就在这。

如果数字逻辑电路的频率达到或者超过45MHZ~50MHZ,而且工作在这个频率之上的电路已经占到了整个电子系统一定的份量(比如说1/3),通常就称为高频电路。高频电路设计是一个非常复杂的设计过程,其布线对整个设计至关重要。

【第一招】多层板布线

在PCB布线规则中,有一条“关键信号线优先”的原则,即电源、摸拟信号、高速信号、时钟信号、差分信号和同步信号等关键信号优先布线。接下来,我们不妨就来详细了解下这些关键信号的布线要求。

1、AD 布蛇形线方法

Tool 里选 Interactive length tuning 要先布好线再改成蛇形,这里用的是布线时直接走蛇形: 先 P->T 布线, 再 Shift + A 切换成蛇形走线

一、概述:

静电释放(ESD)是我们每一个产品设计工程师需要考虑的一个相当重要的问题。大多数电子设备都 处于一个充满ESD的环境之中,ESD可能来自人体、家具甚至设备本身(内部)。电子设备完全遭受ESD损毁比较少见,然而ESD干扰却很常见,它会导致设备锁死、复位、数据丢失和不可靠。其结果可能是:在寒冷干燥的冬季里,电子设备经常出现故障现象,但是维修时又显示正常。

要防止ESD,首先必须知道ESD是什么及ESD进入电子设备的过程。一个充电的导体接近另一个导体时,就可能发生ESD。首先,在2个导体之间会建立一个很强的电场,产生由电场引起的击穿。当2个导体之间的电压超过它们之间空气和绝缘介质的

击穿电压时,就会产生电弧。在0.7ns~10ns的时间里,电弧电流会达到几十A,有时甚至会超过100A。电弧将一直维持,直到2个导体接触短路或者电流低到不能维持电弧为止。

1.1 ESD的产生取决于物体的起始电压、电阻、电感和寄生电容:

● 可能产生电弧的实例有人体、带电器件和机器。

● 可能产生尖峰电弧的实例有手或金属物体。

● 可能产生同极性或极性变化的多个电弧的实例有家具等。

1.常规布线:不详细说了,是个人就知道怎么弄。需要说明的是在布线过程中,可按小键盘的*键或大键盘的数字2键添加一个过孔;按L键可以切换布线层;按数字3可设定最小线宽、典型线宽、最大线宽的值进行切换。