如何突破AI存储墙?深度解析ONFI 6.0高速接口与Chiplet解耦架构

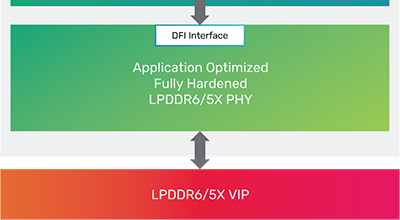

在大模型训练与推理场景中,算力演进速度远超存储带宽,计算与存储之间的性能鸿沟(存储墙)已成为限制系统能效的关键瓶颈。

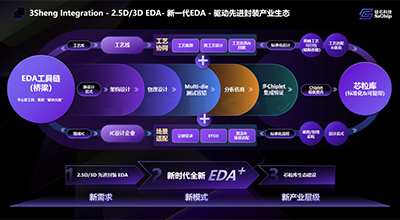

2025年11月17日——中国数字EDA/IP龙头企业上海合见工业软件集团有限公司(简称“合见工软”)与北京芯力技术创新中心有限公司共同宣布,双方正式达成战略合作,共同推进先进封装芯粒(Chiplet)技术的生态建设与产业落地。

当AI算力浪潮席卷全球,芯片设计的边界正延伸至封装层面。政策层面频频强调要加快关键工艺、装备与工业软件的协同创新,推动核心环节自主可控。

随着高性能人工智能算法的快速发展,芯粒(Chiplet)集成系统凭借其满足海量数据传输需求的能力,已成为极具前景的技术方案。该技术能够提供高速互连和大带宽,减少跨封装互连,具备低成本、高性能等显著优势,获得广泛青睐。

硅芯科技自研3Sheng Integration Platform,实现三维堆叠芯片的系统级规划、物理实现与分析、可测性与可靠性设计等,集成“系统-测试-综合-仿真-验证”五引擎合一,具有统一数据底座,支持三维异构集成系统的敏捷开发与可定制化的协同设计优化,并在多个功能和性能上具有独创性。

为了让大家了解Chiplet互联趋势与Die-to-Die接口技术,11月5日晚19点,我们特别邀请到奇异摩尔高级设计经理王彧博士做客贸泽电子芯英雄联盟直播间,与大家展开深入讨论,欢迎预约围观!