随着高性能人工智能算法的快速发展,芯粒(Chiplet)集成系统凭借其满足海量数据传输需求的能力,已成为极具前景的技术方案。该技术能够提供高速互连和大带宽,减少跨封装互连,具备低成本、高性能等显著优势,获得广泛青睐。但芯粒集成中普遍存在供电电流大、散热困难等问题,导致其面临严峻的电迁移可靠性挑战。针对工艺层次高度复杂的芯粒集成系统,如何实现电迁移问题的精确高效仿真,并完成电迁移效应与热效应的耦合分析,已成为先进封装可靠性EDA工具领域的重点研究方向。

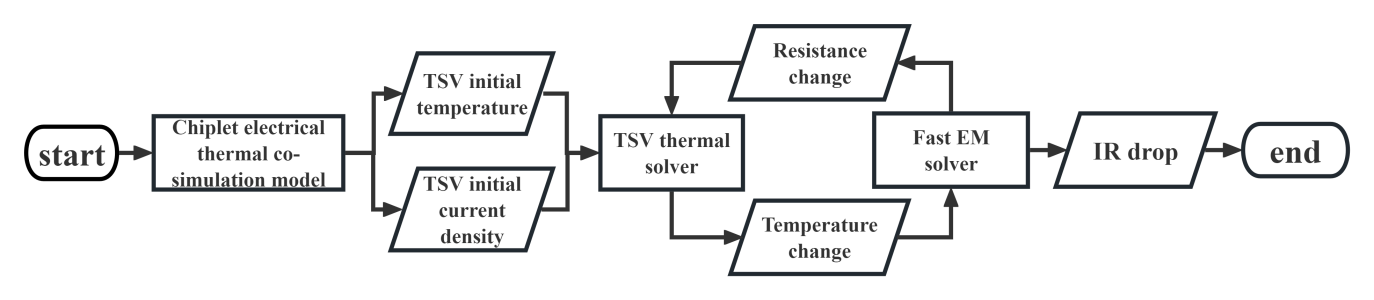

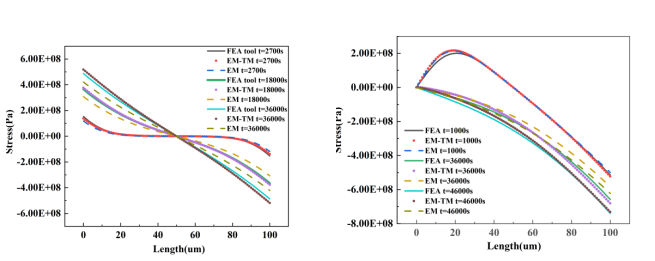

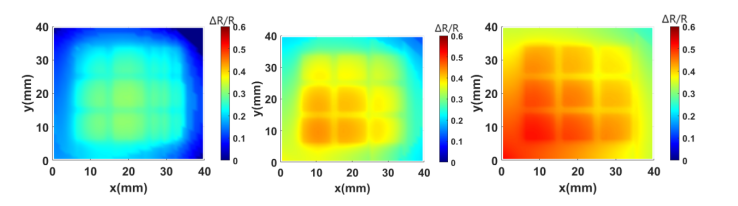

为应对上述挑战,中国科学院微电子研究所EDA中心孙泽宇研究员与徐勤志研究员团队合作开发了一种针对芯粒集成系统中TSV互连的电迁移-热耦合仿真模型。该模型利用时域有限差分法(FDTD),建立了一套涵盖电迁移空洞成核期与完整生长过程的全流程电-热-应力综合分析方法,能够精确计算电子流导致的静水应力。研究还构建了包含散热器的异质集成系统全芯片热模型,应用有限体积元方法(FVM)进行全局电热协同仿真,在严格遵循热传导方程守恒原理的同时,大幅提升了计算效率。尤为关键的是,该模型通过整合电迁移-热迁移与焦耳热效应的仿真,能够在统一框架下解析应力演变、空洞生长、电阻变化和焦耳热效应之间的相互作用机制。模型验证结果表明,与业界商用有限元工具COMSOL相比,仿真误差仅为0.61%;与实验数据相比,其电迁移寿命预测误差较现有主流方法显著降低了76.4%。该模型还能准确反映不同分析阶段温度和电流密度对电迁移过程的主导作用。

此项研究成果以“ChipletEM: Physics-Based 2.5D and 3D Chiplet Heterogeneous Integration Electromigration Signoff Tool Using Coupled Stress and Thermal Simulation”为题,在第62届国际设计自动化会议(DAC)上进行了口头报告。孙泽宇研究员为论文第一作者,徐勤志研究员和微电子所EDA中心李志强研究员为共同通讯作者。该研究工作获得了中国科学院战略性A类先导专项、国家自然科学基金、中国科学院青年交叉团队等项目的资助。

图1:整体电迁移仿真流程

图2:电迁移应力分析结果

图3:不同时间段电迁移整体应力分布

来源:中国科学院微电子研究所